SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

- Advanced LinCMOS™ Silicon-Gate Technology

- 8-Bit Resolution

- Differential Reference Inputs

- Parallel Microprocessor Interface

- Conversion and Access Time Over Temperature Range Read Mode . . . 2.5 μs Max

- No External Clock or Oscillator Components Required

- On-Chip Track and Hold

- Single 5-V Supply

- TLC0820A Is Direct Replacement for National Semiconductor ADC0820C/CC and Analog Devices AD7820K/B/T

### description

The TLC0820AC and the TLC0820AI are Advanced LinCMOS™ 8-bit analog-to-digital converters each consisting of two 4-bit flash converters, a 4-bit digital-to-analog converter, a summing (error) amplifier, control logic, and a result latch circuit. The modified flash technique allows low-power integrated circuitry to complete an 8-bit conversion in 1.18 μs over temperature. The on-chip track-and-hold circuit has a 100-ns sample window and allows these devices to convert continuous analog signals having slew rates of up to 100 mV/μs without external sampling components. TTL-compatible 3-state output drivers and two modes of operation allow

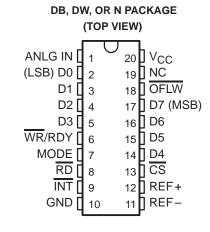

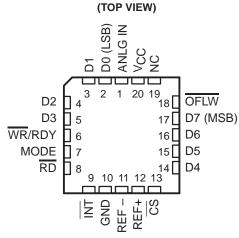

**FN PACKAGE**

NC-No internal connection

interfacing to a variety of microprocessors. Detailed information on interfacing to most popular microprocessors is readily available from the factory.

#### **AVAILABLE OPTIONS**

| TA            | TOTAL               | PACKAGE      |                                  |                                 |                    |  |  |

|---------------|---------------------|--------------|----------------------------------|---------------------------------|--------------------|--|--|

|               | UNADJUSTED<br>ERROR | SSOP<br>(DB) | PLASTIC<br>SMALL OUTLINE<br>(DW) | PLASTIC<br>CHIP CARRIER<br>(FN) | PLASTIC DIP<br>(N) |  |  |

| 0°C to 70°C   | ±1 LSB              | TLC0820ACDB  | TLC0820ACDW                      | TLC0820ACFN                     | TLC0820ACN         |  |  |

| -40°C to 85°C | ±1 LSB              | _            | TLC0820AIDW                      | TLC0820AIFN                     | TLC0820AIN         |  |  |

Advanced LinCMOS is a trademark of Texas Instruments Incorporated.

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

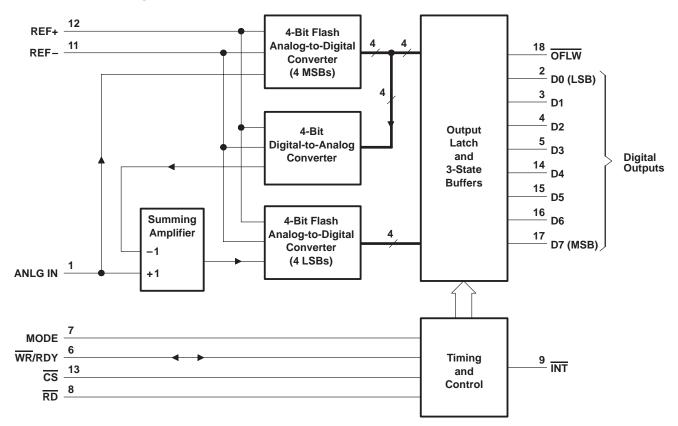

### functional block diagram

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

### **Terminal Functions**

| TERMINAL |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| ANLG IN  | 1   | 1   | Analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| CS       | 13  | ı   | Chip select. CS must be low in order for RD or WR to be recognized by the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| D0       | 2   | 0   | Digital, 3-state output data, bit 1 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| D1       | 3   | 0   | Digital, 3-state output data, bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D2       | 4   | 0   | Digital, 3-state output data, bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D3       | 5   | 0   | Digital, 3-state output data, bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D4       | 14  | 0   | Digital, 3-state output data, bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D5       | 15  | 0   | Digital, 3-state output data, bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D6       | 16  | 0   | Digital, 3-state output data, bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D7       | 17  | 0   | Digital, 3-state output data, bit 8 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| GND      | 10  |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| ĪNT      | 9   | 0   | Interrupt. In the write-read mode, the interrupt output ( $\overline{\text{INT}}$ ) going low indicates that the internal count-down delay time, $t_{d(int)}$ , is complete and the data result is in the output latch. The delay time $t_{d(int)}$ is typically 800 ns starting after the rising edge of $\overline{\text{WR}}$ (see operating characteristics and Figure 3). If $\overline{\text{RD}}$ goes low prior to the end of $t_{d(int)}$ , $\overline{\text{INT}}$ goes low at the end of $t_{d(RL)}$ and the conversion results are available sooner (see Figure 2). $\overline{\text{INT}}$ is reset by the rising edge of either $\overline{\text{RD}}$ or $\overline{\text{CS}}$ .        |  |  |  |  |

| MODE     | 7   | I   | Mode select. MODE is internally tied to GND through a 50-μA current source, which acts like a pulldown resistor. When MODE is low, the read mode is selected. When MODE is high, the write-read mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| NC       | 19  |     | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

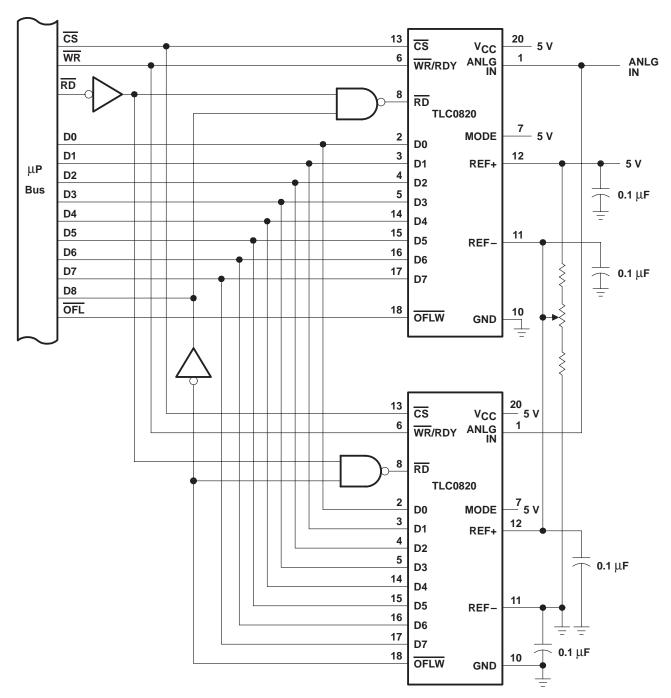

| OFLW     | 18  | 0   | Overflow. Normally OFLW is a logical high. However, if the analog input is higher than V <sub>fef+</sub> , OFLW will be low at the end of conversion. It can be used to cascade two or more devices to improve resolution (9 or 10 bits).                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| RD       | 8   | I   | Read. In the write-read mode with $\overline{CS}$ low, the 3-state data outputs D0 through D7 are activated when $\overline{RD}$ goes low. $\overline{RD}$ can also be used to increase the conversion speed by reading data prior to the end of the internal count-down delay time. As a result, the data transferred to the output latch is latched after the falling edge of $\overline{RD}$ . In the read mode with $\overline{CS}$ low, the conversion starts with $\overline{RD}$ going low. $\overline{RD}$ also enables the 3-state data outputs on completion of the conversion. RDY going into the high-impedance state and $\overline{INT}$ going low indicate completion of the conversion. |  |  |  |  |

| REF-     | 11  | I   | Reference voltage. REF – is placed on the bottom of the resistor ladder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| REF+     | 12  | I   | Reference voltage. REF+ is placed on the top of the resistor ladder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| VCC      | 20  |     | Power supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| WR/RDY   | 6   | I/O | Write ready. In the write-read mode with $\overline{CS}$ low, the conversion is started on the falling edge of the $\overline{WR}$ input signal. The result of the conversion is strobed into the output latch after the internal count-down delay time, $t_{d(int)}$ , provided that the $\overline{RD}$ input does not go low prior to this time. The delay time $t_{d(int)}$ is approximately 800 ns. In the read mode, RDY (an open-drain output) goes low after the falling edge of $\overline{CS}$ and goes into the high-impedance state when the conversion is strobed into the output latch. It is used to simplify the interface to a microprocessor system.                                  |  |  |  |  |

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>CC</sub> (see Note 1)                                   | 10 V                                                |

|--------------------------------------------------------------------------------|-----------------------------------------------------|

| Input voltage range, all inputs (see Note 1)                                   | $-0.2\ V$ to $V_{\mbox{\footnotesize CC}} + 0.2\ V$ |

| Output voltage range, all outputs (see Note 1)                                 | $-0.2\ V$ to $V_{\mbox{\footnotesize CC}} + 0.2\ V$ |

| Operating free-air temperature range: TLC0820AC                                | 0°C to 70°C                                         |

| TLC0820AI                                                                      | $-40^{\circ}$ C to $85^{\circ}$ C                   |

| Storage temperature range                                                      | $\dots$ -65°C to 150°C                              |

| Case temperature for 10 seconds: FN package                                    | 260°C                                               |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: DB, DW or N pacl | kage 260°C                                          |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltages are with respect to network GND.

### recommended operating conditions

|                                                                                       |                                    |                | MIN | NOM | MAX                  | UNIT |

|---------------------------------------------------------------------------------------|------------------------------------|----------------|-----|-----|----------------------|------|

| Supply voltage, V <sub>CC</sub>                                                       |                                    |                |     |     | 8                    | V    |

| Analog input voltage                                                                  |                                    |                |     |     | V <sub>CC</sub> +0.1 | V    |

| Positive reference voltage, V <sub>ref+</sub>                                         |                                    |                |     |     | VCC                  | V    |

| Negative reference voltage, V <sub>ref</sub> _                                        |                                    |                |     |     | V <sub>ref+</sub>    | V    |

| High level input valtage VIII                                                         | V <sub>CC</sub> = 4.75 V to 5.25 V | CS, WR/RDY, RD | 2   |     |                      | V    |

| High-level input voltage, V <sub>IH</sub>                                             |                                    | MODE           | 3.5 |     |                      | 1 °  |

| Low level input voltage. Viv                                                          | V <sub>CC</sub> = 4.75 V to 5.25 V | CS, WR/RDY, RD |     |     | 0.8                  | V    |

| Low-level input voltage, V <sub>IL</sub>                                              |                                    | MODE           |     |     | 1.5                  | V    |

| Pulse duration, write in write-read mode, t <sub>W(W)</sub> (see Figures 2, 3, and 4) |                                    |                |     |     | 50                   | μs   |

| Operating two air temperature T.                                                      | TLC0820AC                          |                | 0   |     | 70                   | °C   |

| Operating free-air temperature, T <sub>A</sub>                                        | TLC0820AI                          |                | -40 |     | 85                   | -0   |

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

# electrical characteristics at specified operating free-air temperature, $V_{CC} = 5 \text{ V}$ (unless otherwise noted)

|                                       | PARAMETER                                       |                             | TEST CONDITIONS                                                                                       | T <sub>A</sub> † | MIN   | TYP    | MAX  | UNIT |

|---------------------------------------|-------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------|------------------|-------|--------|------|------|

| Vон                                   | High-level output voltage                       | D0-D7, ĪNT, or OFLW         | $V_{CC} = 4.75 \text{ V},$ $I_{OH} = -360 \mu\text{A}$                                                | Full range       | 2.4   |        |      | .,   |

|                                       |                                                 |                             | V <sub>CC</sub> = 4.75 V,                                                                             | Full range       | 4.5   |        |      | V    |

|                                       |                                                 |                             | I <sub>OH</sub> = -10 μA                                                                              | 25°C             | 4.6   |        |      |      |

| Vol                                   | Low-level output voltage                        | D0_D7, OFLW, INT, or WR/RDY | V <sub>CC</sub> = 5.25 V,<br>I <sub>OL</sub> = 1.6 mA                                                 | Full range       |       |        | 0.4  | ٧    |

| VOL                                   | Low-level output voltage                        |                             |                                                                                                       | 25°C             |       |        | 0.34 | V    |

|                                       |                                                 | CS or RD                    | ]                                                                                                     | Full range       |       | 0.005  | 1    |      |

|                                       |                                                 | WR/RDY                      |                                                                                                       | Full range       |       |        | 3    |      |

| lіН                                   | High-level input current                        | WICKET                      | V <sub>IH</sub> = 5 V                                                                                 | 25°C             |       | 0.1    | 0.3  | μΑ   |

|                                       |                                                 | MODE                        |                                                                                                       | Full range       |       |        | 200  |      |

|                                       |                                                 |                             |                                                                                                       | 25°C             |       | 50     | 170  |      |

| I <sub>IL</sub>                       | Low-level input current                         | CS, WR/RDY, RD, or MODE     | V <sub>IL</sub> = 0                                                                                   | Full range       |       | -0.005 | -1   | μΑ   |

|                                       |                                                 |                             | V <sub>O</sub> = 5 V                                                                                  | Full range       |       |        | 3    | μΑ   |

|                                       | Off-state (high-impedance-state) output current | D0-D7 or WR/RDY             |                                                                                                       | 25°C             |       | 0.1    | 0.3  |      |

| loz                                   |                                                 | DU-D7 or WR/RDY             | V <sub>O</sub> = 0                                                                                    | Full range       |       |        | -3   |      |

|                                       |                                                 |                             |                                                                                                       | 25°C             |       | -0.1   | -0.3 |      |

|                                       |                                                 |                             | $CS \text{ at 5 V},  V_{I} = 5 \text{ V} \qquad \begin{array}{ c c c c c c c c c c c c c c c c c c c$ |                  |       | 3      |      |      |

| ١.                                    | Analog input current                            |                             |                                                                                                       | 25°C             |       |        | 0.3  | μΑ   |

| l <sub>l</sub>                        | Analog input current                            |                             |                                                                                                       | Full range       |       |        | -3   |      |

|                                       |                                                 |                             |                                                                                                       | 25°C             |       |        | -0.3 |      |

|                                       |                                                 | D0-D7, OFLW, INT, or WR/RDY | V <sub>O</sub> = 5 V                                                                                  | Full range       | 7     |        |      |      |

|                                       |                                                 |                             |                                                                                                       | 25°C             | 8.4   | 14     |      | ]    |

| loo                                   | Short-circuit output current                    | D0-D7 or OFLW               |                                                                                                       | Full range       | -6    |        |      | mΛ   |

| los                                   | Short-circuit output current                    | DU-D7 OF OFLW               | V <sub>O</sub> = 0                                                                                    | 25°C             | -7.2  | -12    |      | mA   |

|                                       |                                                 | INT                         | ] VO = 0                                                                                              | Full range       | -4.5  |        |      |      |

|                                       |                                                 | IIVI                        |                                                                                                       | 25°C             | - 5.3 | -9     |      |      |

| ъ,                                    | Reference resistance                            |                             |                                                                                                       | Full range       | 1.25  |        | 6    | kΩ   |

| R <sub>ref</sub> Reference resistance |                                                 |                             |                                                                                                       | 25°C             | 1.4   | 2.3    | 5.3  | K22  |

| loc                                   | Cumby current                                   |                             | CS, WR/RDY, and RD at 0 V                                                                             | Full range       |       |        | 15   | mA   |

| ICC                                   | Supply current                                  |                             | RD at 0 V                                                                                             | 25°C             |       | 7.5    | 13   | 111/ |

| C.                                    | Input capacitance                               | D0-D7                       |                                                                                                       | Full range       |       | 5      |      | pF   |

| Ci                                    | Input capacitance                               | ANLG IN                     |                                                                                                       | i uli rarige     |       | 45     |      | ρı   |

| Co                                    | Output capacitance                              | D0-D7                       |                                                                                                       | Full range       |       |        | 5    | pF   |

<sup>†</sup> Full range is as specified in recommended operating conditions.

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

# operating characteristics, $V_{CC}$ = 5 V, $V_{ref+}$ = 5 V, $V_{ref-}$ = 0, $t_r$ = $t_f$ = 20 ns, $T_A$ = 25°C (unless otherwise noted)

|                      | PARAMETER                                       | TEST                                        | CONDITIONS†                                                     | MIN              | TYP         | MAX             | UNIT |

|----------------------|-------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------|------------------|-------------|-----------------|------|

| ksvs                 | Supply-voltage sensitivity                      | $V_{CC} = 5 V \pm 5\%$ ,                    | $T_A = MIN \text{ to } MAX$                                     | ±                | 1/16        | ±1/4            | LSB  |

|                      | Total unadjusted error‡                         | MODE at 0 V,                                | $T_A = MIN \text{ to } MAX$                                     |                  |             | 1               | LSB  |

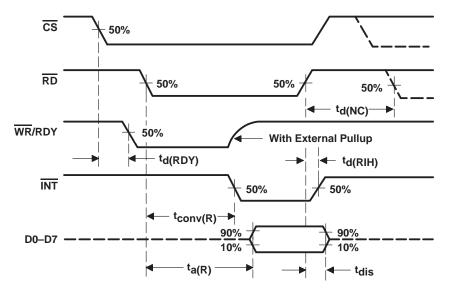

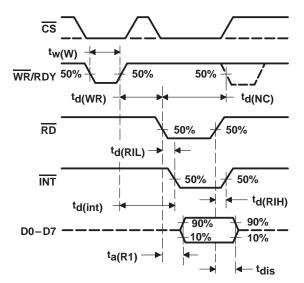

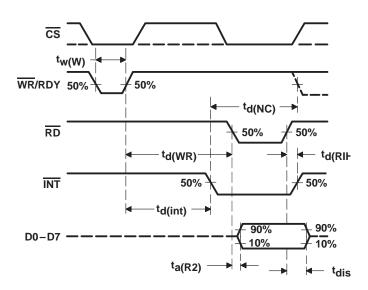

| tconv(R)             | Conversion time, read mode                      | MODE at 0 V,                                | See Figure 1                                                    |                  | 1.6         | 2.5             | μs   |

| <sup>t</sup> a(R)    | Access time, RD↓ to data valid                  | MODE at 0 V,                                | See Figure 1                                                    | t <sub>con</sub> | v(R)<br>+20 | tconv(R)<br>+50 | ns   |

|                      | . = . =                                         | MODE at 5 V,                                | C <sub>L</sub> = 15 pF                                          |                  | 190         | 280             |      |

| <sup>t</sup> a(R1)   | Access time, RD↓ to data valid                  | td(WR) < td(int),<br>See Figure 2           | C <sub>L</sub> = 100 pF                                         |                  | 210         | 320             | ns   |

| 4                    | Access Core DD to determine                     | MODE at 5 V,                                | C <sub>L</sub> = 15 pF                                          |                  | 70          | 120             |      |

| ta(R2)               | Access time, RD↓ to data valid                  | td(WR) > td(int),<br>See Figure 3           | C <sub>L</sub> = 100 pF                                         |                  | 90          | 150             | ns   |

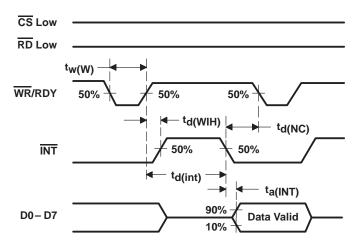

| ta(INT)              | Access time, INT ↓ to data valid                | MODE at 5 V,                                | See Figure 4                                                    |                  | 20          | 50              | ns   |

| t <sub>dis</sub>     | Disable time, RD↑ to data valid                 | R <sub>L</sub> = 1 kΩ,<br>See Figures 1, 2, | C <sub>L</sub> = 10 pF,<br>3, and 5                             |                  | 70          | 95              | ns   |

| <sup>t</sup> d(int)  | Delay time, WR/RDY↑ to INT↓                     | MODE at 5 V,<br>See Figures 2, 3,           | MODE at 5 V, C <sub>L</sub> = 50 pF,<br>See Figures 2, 3, and 4 |                  | 800         | 1300            | ns   |

| t <sub>d</sub> (NC)  | Delay time, to next conversion                  | See Figures 1, 2,                           | See Figures 1, 2, 3, and 4                                      |                  |             |                 | ns   |

| t <sub>d(WR)</sub>   | Delay time, WR/RDY↑ to RD↓ in write-read mode   | See Figure 2                                |                                                                 | 0.4              |             |                 | μs   |

| <sup>t</sup> d(RDY)  | Delay time, CS↓ to WR/RDY↓                      | MODE at 0 V,<br>See Figure 1                | C <sub>L</sub> = 50 pF,                                         |                  | 50          | 100             | ns   |

| t <sub>d</sub> (RIH) | Delay time, RD↑ to INT↑                         | C <sub>L</sub> = 50 pF,                     | See Figures 1, 2, and 3                                         |                  | 125         | 225             | ns   |

| td(RIL)              | Delay time, RD $\downarrow$ to INT $\downarrow$ | MODE at 5 V,<br>See Figure 2                | $t_{d(WR)} < t_{d(int)}$                                        |                  | 200         | 290             | ns   |

| td(WIH)              | Delay time, WR/RDY↑ to INT↑                     | MODE at 5 V,<br>See Figure 4                | C <sub>L</sub> = 50 pF,                                         |                  | 175         | 270             | ns   |

|                      | Slew-rate tracking                              |                                             |                                                                 |                  | 0.1         |                 | V/µs |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>‡</sup> Total unadjusted error includes offset, full-scale, and linearity errors.

### PARAMETER MEASUREMENT INFORMATION

Figure 1. Read-Mode Waveforms (MODE Low)

Figure 2. Write-Read-Mode Waveforms [MODE High and t<sub>d(WR)</sub> < t<sub>d(int)</sub>]

Figure 3. Write-Read-Mode Waveforms [MODE High and  $t_{d(WR)} > t_{d(int)}$ ]

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

### PARAMETER MEASUREMENT INFORMATION

Figure 4. Write-Read-Mode Waveforms (Stand-Alone Operation, MODE High, and RD Low)

Figure 5. Test Circuit and Voltage Waveforms

SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

### PRINCIPLES OF OPERATION

The TLC0820AC and TLC0820AI each employ a combination of sampled-data comparator techniques and flash techniques common to many high-speed converters. Two 4-bit flash analog-to-digital conversions are used to give a full 8-bit output.

The recommended analog input voltage range for conversion is -0.1 V to  $V_{CC} + 0.1 \text{ V}$ . Analog input signals that are less than  $V_{ref-} + 1/2 \text{ LSB}$  or greater than  $V_{ref+} - 1/2 \text{ LSB}$  convert to 00000000 or 111111111, respectively. The reference inputs are fully differential with common-mode limits defined by the supply rails. The reference input values define the full-scale range of the analog input. This allows the gain of the ADC to be varied for ratiometric conversion by changing the  $V_{ref-}$  and  $V_{ref-}$  voltages.

The device operates in two modes, read (only) and write-read, that are selected by MODE. The converter is set to the read (only) mode when MODE is low. In the read mode,  $\overline{WR}/RDY$  is used as an output and is referred to as the ready terminal. In this mode, a low on  $\overline{WR}/RDY$  while  $\overline{CS}$  is low indicates that the device is busy. Conversion starts on the falling edge of  $\overline{RD}$  and is completed no more than 2.5  $\mu$ s later when  $\overline{INT}$  falls and  $\overline{WR}/RDY$  returns to the high-impedance state. Data outputs also change from high-impedance to active states at this time. After the data is read,  $\overline{RD}$  is taken high,  $\overline{INT}$  returns high, and the data outputs return to their high-impedance states.

When MODE is high, the converter is set to the write-read mode and  $\overline{WR}/RDY$  is referred to as the write terminal. Taking  $\overline{CS}$  and  $\overline{WR}/RDY$  low selects the converter and initiates measurement of the input signal. Approximately 600 ns after  $\overline{WR}/RDY$  returns high, the conversion is completed. Conversion starts on the rising edge of  $\overline{WR}/RDY$  in the write-read mode.

The high-order 4-bit flash ADC measures the input by means of 16 comparators operating simultaneously. A high-precision 4-bit DAC then generates a discrete analog voltage from the result of that conversion. After a time delay, a second bank of comparators does a low-order conversion on the analog difference between the input level and the high-order DAC output. The results from each of these conversions enter an 8-bit latch and are output to the 3-state output buffers on the falling edge of  $\overline{RD}$ .

### SLAS064A - SEPTEMBER 1986 - REVISED JUNE 1994

### **APPLICATION INFORMATION**

Figure 6. Configuration for 9-Bit Resolution

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated